近期,我院解光军教授课题组在随机计算和量子元胞自动机电路设计方面取得重要进展。随着CMOS技术持续向更小的尺度发展,摩尔定律已走向物理极限。随机计算和量子元胞自动机被认为是超越摩尔定律的有效方法。

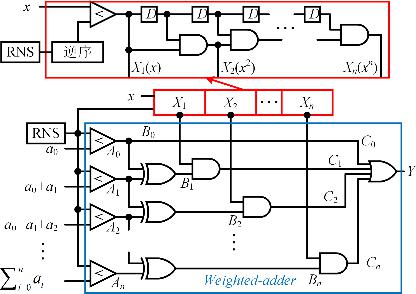

针对图像处理、神经网络等应用,精确的二进制计算方法需要消耗大量的硬件资源与能耗。而对于这些容错性应用,精确计算往往是非必须的。课题组提出利用硬线连接和最优序列设计随机乘法器来降低资源开销,并在图像相乘、图像平滑等应用中进行验证。仿真实验结果表明,该方案设计的6位乘法器即可保证处理后的图像的峰值信噪比高于30dB。

该工作于2023年2月以“Highly Accurate and Energy Efficient Binary-Stochastic Multipliers for Fault-Tolerant Applications”为题发表在IEEE Transactions on Circuits and Systems II: Express Briefs。合肥工业大学为第一署名单位,加拿大阿尔伯塔大学为合作单位,张永强老师为本文第一作者,解光军教授为本文通讯作者。论文链接:https://ieeexplore.ieee.org/document/9903912/

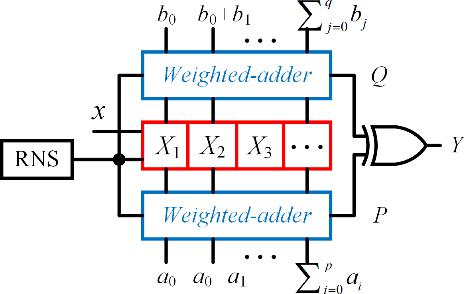

为进一步提高随机乘法器的计算精度,课题组提出利用数值分割法和确定性随机比特流来设计乘法器,通过在AlexNet网络上对CIFAR10数据集进行识别来验证设计方案。仿真实验结果表明,在保证精度的前提下,该设计方案能有效降低电路所需的能耗资源。

该工作于2023年2月以“An Energy-Efficient Binary-Interfaced Stochastic Multiplier Using Parallel Datapaths”为题发表在IEEE Transactions on Very Large Scale Integration (VLSI) Systems。合肥工业大学为第一署名单位,上海科技大学和加拿大阿尔伯塔大学为合作单位,张永强老师为本文第一作者,解光军教授为本文通讯作者。论文链接:https://ieeexplore.ieee.org/document/10056859/

传统的DSP是基于CPU结构,随着运算时钟越来越接近电子器件可以接受的界限,DSP的处理能力也在接近极限。课题组提出利用随机比特流相关度直接设计多项式运算电路,能够很好地处理多种比较复杂的函数。仿真实验结果表明,该设计方案不仅资源开销低,与当前报道的随机设计方案相比,均方误差能够降低69%。

该工作于2022年10月以“Weighted-Adder-Based Polynomial Computation Using Correlated Unipolar Stochastic Bitstreams”为题发表在IEEE Transactions on Circuits and Systems II: Express Briefs。合肥工业大学为唯一署名单位,博士研究生王少威为本文第一作者,张永强老师为本文通讯作者。论文链接:https://ieeexplore.ieee.org/document/9843901/

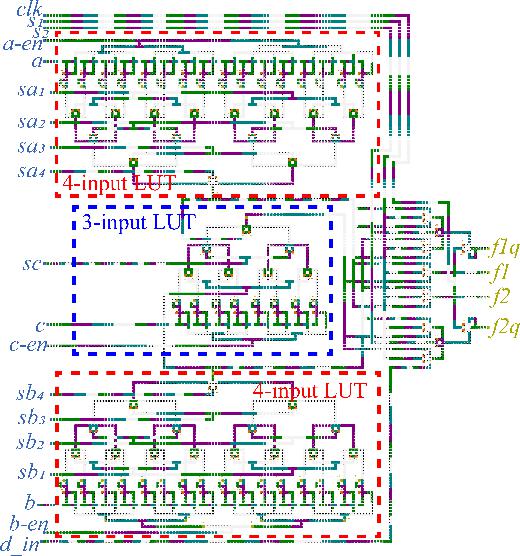

量子元胞自动机电路具有高集成度、低功耗和无引线集成等优势。课题组提出利用量子元胞自动机特有的时钟机制设计CLB。仿真实验结果表明,该方案设计的CLB的功耗仅4.69×10^-7mW,远低于基于CMOS技术的设计方案。

该工作于2022年8月以“Design and Implementation of SRAM for LUT and CLB Using Clocking Mechanism in Quantum-Dot Cellular Automata”为题发表在IEEE Transactions on Circuits and Systems II: Express Briefs。合肥工业大学为唯一署名单位,张永强老师为本文第一作者,解光军教授为本文通讯作者。论文链接:https://ieeexplore.ieee.org/document/9766174/

(张永强/文/图 赵金华/审核)