——面向长距多媒体传输的SerDes及高性能时钟芯片产品研发

芯片设计作为多学科交叉的高复杂性领域,要求工程师同时具备扎实的理论基础(如半导体物理、晶体管级电路分析)、精准的工艺认知(如CMOS工艺角参数影响、ESD设计考量)和系统的工程思维(如噪声与功耗的折衷优化),这类能力往往需要结合全流程实践而非单纯的课堂教育才能获取。产学研用的教育模式通过"企业需求牵引-学校理论深化-产线验证闭环"的三维体系,使学生在真实项目中掌握关键能力:比如,在基准电路设计中理解蒙特卡罗仿真与实测误差的来源及对应关系,在时钟芯片开发中完成从Spec定义、系统建模到版图后仿真和硅验证的全流程,通过"理论-实践-迭代"的螺旋式上升过程,培养出直接匹配企业需求的实战型人才。

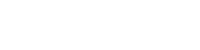

孟煦课题组近年来在维持学术前沿探索的同时,坚持落实产学研用的培养模式,与中电科五十八所(中科芯集成电路)、山海半导体、合肥汤诚集成等公司开展面向芯片产品的深度合作,成功研发多款芯片并实现了硕士研究生们在学习和就业上与合作公司的“无缝衔接”。其中,与中科芯年均合作2至3项科研项目,成功量产多款芯片产品;得获对方评为“最佳合作团队”并成立了联合培养基地等。课题组主要在下述领域展开了研究:

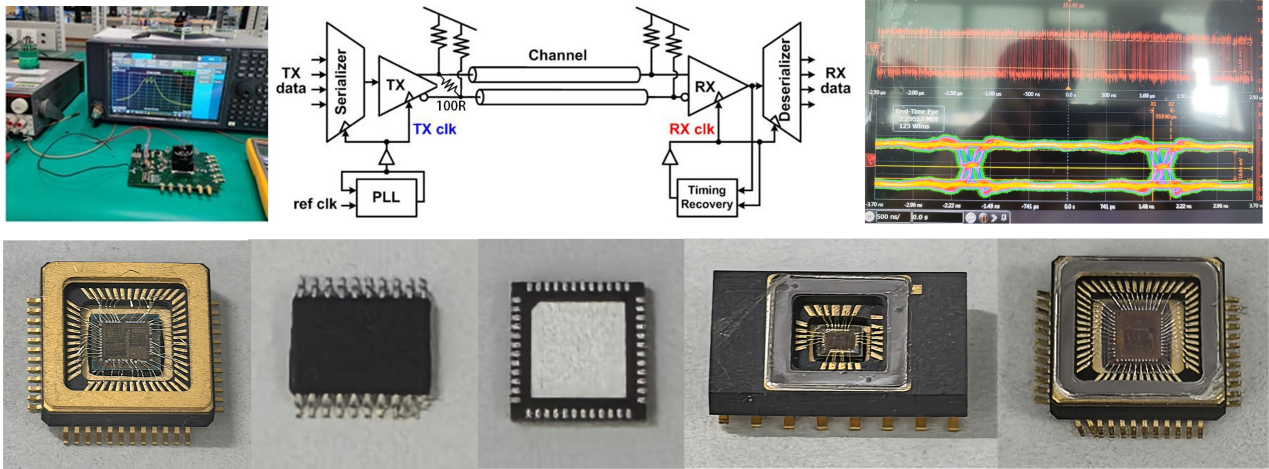

(1)SerDes(串行器/解串器)技术通过将并行数据转化为高速串行流,在芯片间、板卡间乃至设备间构建起高效传输通道。而当技术谱系延伸至车载领域,SerDes面临更具挑战的工程约束:在面向智能驾驶"传感器-计算单元-显示屏"的信号链中,需要克服15米以上线缆的高频衰减、发动机舱的电磁干扰,以及多节点同步的时序收敛等问题。课题组已协助合作单位在国产工艺上实现了展频参考时钟芯片和Gbps长距离SerDes芯片的量产,完成了面向1080p视频传输的3Gbps长距离SerDes芯片的投片测试等,并已开展面向12Gbps长距离SerDes芯片的项目研发。

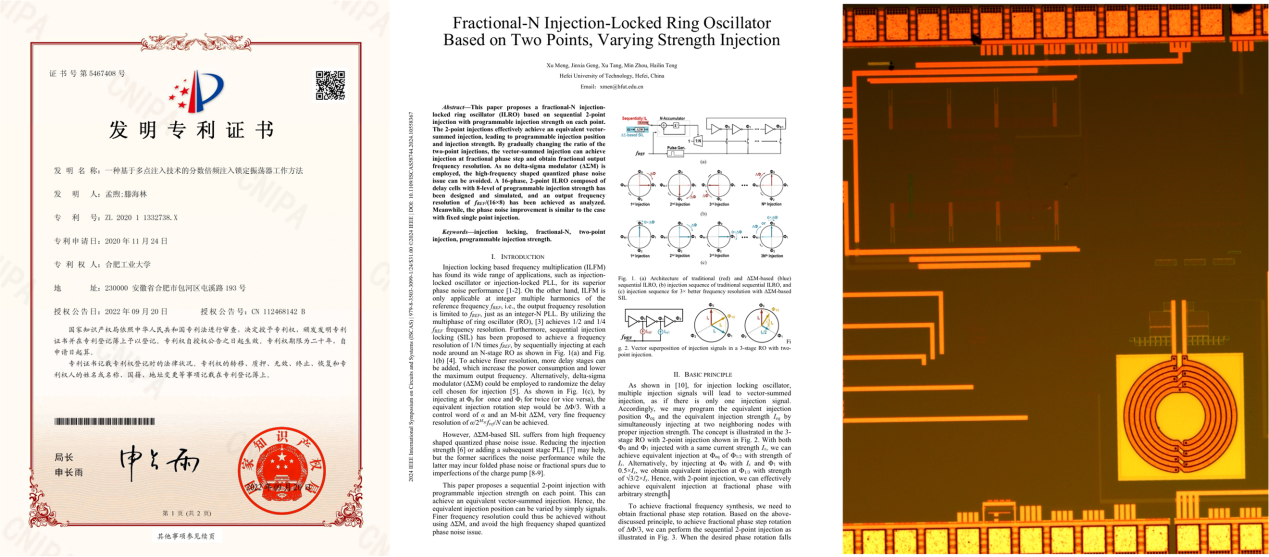

(2)时钟信号的质量对各类处理器和无线/有线通信系统的性能起着至关重要的作用。课题组在对标研发各类高性能时钟芯片的同时,依托所主持的国家重点研发计划子课题和国家自然科学基金项目,结合实际应用场景,创新性的提出了两点、变强度注入锁定技术,在时钟产生和驱动方面具有极佳的应用前景;相关技术已注册专利并在在IEEE ISCAS会议上汇报。此外,通过多个产业项目的积累,课题组具备了在28nm-350nm各个工艺节点下定制设计可量产高性能时钟芯片的能力。

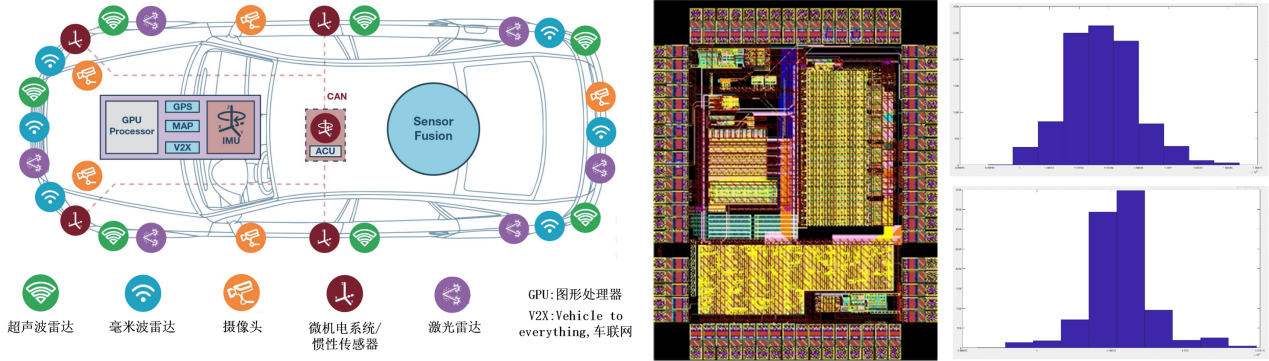

(3)为了实现L5级别的自动无人驾驶,除了基于摄像头和数据传输的“视觉”系统外,基于毫米波雷达和激光雷达的“感知”系统亦不可或缺。课题组近年来已陆续完成了面向77GHz毫米波雷达FMCW PLL的设计,应用于激光雷达高精度飞行时间测量TDC芯片的研发测试,以及应用于车载通信的高速CAN收发器芯片的设计投片,后续将进一步结合应用、探究高性能测量/测距芯片的研发工作。

(孟煦/文/图 张发宇/审核)