容错设计的目的是确保电路与系统在出现故障或错误时能够继续运行,并且能够在一定程度上保持稳定性,已成为一个重要的研究和实践领域,其核心思想是通过将电路与系统分解为多个组件,并为每个组件实现故障检测和故障恢复机制,从而确保整个系统能够在出现故障时继续运行。我院集成电路容错设计与EDA技术闫爱斌团队在国家自然科学基金国际合作以及面上和青年项目、安徽省杰出青年人才项目等支持下,系统研究了宇航级存储电路的抗软错误方法,设计了3D芯片硅通孔抗制造缺陷导致簇故障的容错方案,并研发了配套的EDA软件。

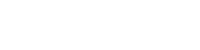

(1)宇航级存储芯片抗单粒子效应导致软错误的设计方法

战略航天器是大国重器,每一个航天器都配备电子装备系统,宇航级芯片即是宇航电子装备的心脏,而锁存器等则是宇航级存储芯片必不可少的组成部件。宇航环境下,辐射效应会致使存储部件发生诸如多节点翻转、故障脉冲等软错误。针对宇航环境下辐射致使存储部件发生软错误的问题,团队提出了一系列高可靠性、低开销、以及可靠性和开销有效折中的宇航级存储电路容错设计方法,具有多节点翻转容忍或自恢复、协同过滤故障脉冲,以及与开销有效折中的技术特点。主要创新点和学术贡献包括:

1)开销有效的抗三节点翻转/过滤故障脉冲的锁存器设计。针对宇航级存储电路高可靠与低开销的需求,提出田型存储和二级过滤结构,构造了开销显著低并抗三节点翻转的锁存器,提出的三模汇聚无表决方案解决了输出端高阻态和协同过滤脉冲的问题,实验验证了其可靠性与低开销。

2)高可靠性的抗四节点翻转的锁存器设计。针对“范艾伦辐射带”等强辐射环境导致电路发生四节点翻转的问题,设计了容忍任意四节点翻转的锁存器,基于隔离DICE和多级拦截C单元进行了电路实现,实验验证了其四节点翻转容忍能力,并且兼顾了其硅面积和传输延迟开销。

3)可靠性和开销折中的软错误在线自恢复的锁存器设计。针对软错误不恢复即会累积并兼顾开销的问题,首先设计了双节点翻转自恢复的锁存器,使用高速路径提高了性能,然后设计了任意三节点翻转在线自恢复的锁存器,实验验证了它们的可靠性和开销达到了有效折中。

该方向近五年研究成果发表在IEEE TC、TAES(11篇、其中2篇ESI高被引)、TCAS-I(2篇)、TETC(3篇、其中2篇ESI高被引)等期刊上;获授权发明专利8项;获IEEE ITC-Asia2023最佳论文奖1项、IEEE AsianHOST2022最佳论文奖1项、ACM GLSVLSI2022最佳论文提名奖1项。上述研究成果为宇航级存储芯片抗软错误提供了新的思路。

图1 提出的节点翻转二级过滤锁存器、三模汇聚无表决锁存器、多翻转自恢复锁存器与蜂窝式硅通孔容错方案

(2)3D芯片硅通孔抗制造缺陷导致簇故障的容错设计

芯片在早夭期失效率高,主要由制造缺陷导致,由于晶片减薄及硅片表面粗糙性,在3D硅片绑定过程中,硅通孔质量会变差。一个硅通孔在其制造过程中若出现缺陷,则在其附近的硅通孔发生缺陷的概率会增加(缺陷聚集为簇故障)显著降低了3D芯片制造良率,抗簇故障的3D芯片硅通孔容错设计面临严峻挑战。针对制造缺陷导致簇故障的问题,提出了数款3D芯片硅通孔抗簇故障设计方法,具有簇故障修复率高、无需使用冗余硅通孔、与硬件和延迟开销有效折中的技术特点。主要创新点和学术贡献包括:

1)修复率与开销有效折中的蜂窝式硅通孔冗余容错方案。针对簇故障修复率与开销需协同考虑的问题,将冗余硅通孔布局在蜂窝结构外侧,设计了蜂窝式硅通孔冗余容错方案,提出了“簇故障聚集窗口”综合评价指标,达到了硬件开销延迟开销和高修复率的有效折中。

2)开销有效的硅通孔簇故障容错方案。针对开销优先的设计需求,设计了不需要使用冗余硅通孔的簇故障容错方案,提出了路由算法有效避过出错硅通孔进行容错,保证了高修复率,与基于路由的、基于环的、基于组的和基于传统蜂窝的硅通孔容错方法相比,降低了硬件和延迟开销。

3)硅通孔全生命期可靠性增强方案。针对硅通孔全生命期可靠性加强的需求,提出了时分复用硅通孔技术,构建了生命期可靠性增强模型,计算并增强了硅通孔全生命期可靠性,改善了信号路由自由度,降低了硬件和延迟开销,实验验证了工作十年后可靠性的保持能力。

该方向近五年研究成果发表在IEEE TVLSI(ESI高被引、他引154次)、TCAD(ESI高被引)、TETC(ESI高被引)等期刊上。上述成果为该方向的研究起到了开创性作用。

(3)与集成电路设计配套的EDA软件研发

开发了锁存器仿真源码自动生成、电路多节点翻转自恢复性验证、电路软错误率图形化显示等EDA软件,具有自动生成锁存器仿真源码、自动提取仿真数据、自动验证电路是否具有多节点翻转自恢复功能、自动化显示电路软错误率等特点。主要创新点和学术贡献包括:

图2 锁存器仿真源码自动生成、容错自动化验证与软错误率图形化显示EDA软件

1)锁存器仿真源码自动生成EDA软件开发。针对人工编写锁存器仿真源码导致编码速度慢、准确率低,影响工作效率的问题,开发了锁存器仿真源码自动生成EDA软件工具,具有典型和自定义锁存器的仿真源码自动生成、仿真结果提取和图像显示等功能,提高了锁存器的设计效率和质量。

2)多节点翻转自恢复性验证EDA软件开发。针对传统软错误恢复验证方法高度依赖于EDA工具,需要进行复杂组合的故障注入,导致漏检并误判电路容错能力的问题,开发了验证多节点翻转在线自恢复性的EDA软件,取得了与进口EDA软件相同的验证结果,提高了电路的验证效率和质量。

3)电路软错误率图形化显示EDA软件开发。针对现有软错误率计算软件的评估结果显示不直观,影响软错误率排序工作效率的问题,开发了电路软错误率图形化显示EDA软件,具有预置基准电路软错误率计算与排序功能,将器件软错误率按序着色,提高了软错误率的显示度和工作效率。

该方向近五年研究成果发表在IEEE TCAD(4篇、其中1篇ESI高被引)等国际期刊上,并开发了配套EDA软件。上述成果为电路自动化设计验证与图形化显示提供了重要的实验指导。

图3各种证书证明