近日,我院解光军教授、张章教授团队,在面向智能语音识别等音频应用的高性能ADC芯片设计领域取得重要研究进展。团队针对制约音频ADC性能的核心难题,创新性地提出了一种“双向推进数据加权平均(Bi-ADWA)”技术,成功设计并流片实现了一款关键性能达到国际先进水平的连续时间Delta-Sigma调制器芯片。相关研究成果以“A 109-dB SFDR Continuous-Time Delta-Sigma Modulator for Audio Using Bi-Directional Advancing Data Weighted Averaging”为题,于2025年11月已被集成电路领域国际著名期刊《IEEE Transactions on Circuits and Systems II: Express Briefs》接收并在线发表。

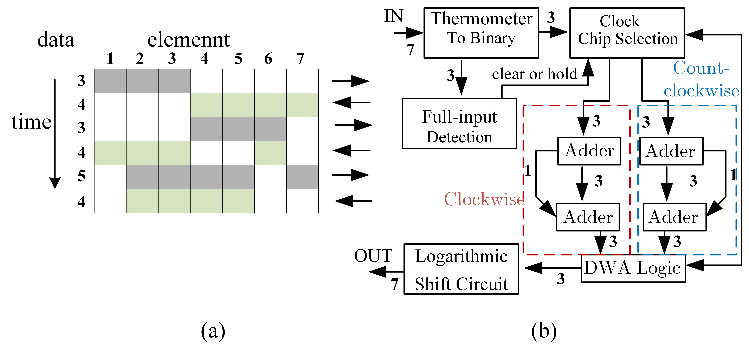

ADC是芯片中连接物理世界模拟信号与数字处理系统的核心桥梁,其核心价值在于将连续的真实世界模拟信号转为数字系统可处理的二进制数据 —— 没有 ADC,数字芯片便无法感知真实环境,而其性能直接决定芯片的感知精度、信号纯净度与应用上限,是支撑各类芯片功能落地与技术升级的“入口基石”,适配消费电子、工业控制等全场景。连续时间Delta-Sigma调制器因其高效能和强抗干扰性,成为主流音频ADC方案。然而,其内部数模转换器(DAC)的元件失配会导致信号失真,影响音质。传统校准技术虽能减轻失真,但会带来新的杂音干扰。为解决这一问题,研究团队提出新型Bi-ADWA算法。该技术通过改变DAC单元的使用顺序,将失真成分转移至人耳听不到的高频区域,从而在音频主频段内获得纯净信号。仿真结果显示,该算法性能显著优于现有技术。

图1所提出的Bi-ADWA算法原理及流程图

基于该创新算法,团队采用180 nm CMOS工艺成功流片并完成了芯片测试。测试结果验证了设计的卓越性能:该调制器在20 kHz音频带宽内,实现了102.5 dB的动态范围(DR)和95.8 dB的峰值信噪失真比(SNDR),值得一提的是,其无杂散动态范围(SFDR)高达109 dB,显著提升了音频信号的质量。芯片在1.8V电压下工作功耗仅为0.58 mW,核心面积0.8 mm²,其综合性能指标(Schreier优值)达到177.9 dB,处于国际领先水平。

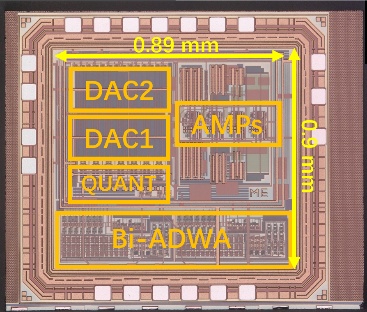

图2芯片显微镜图

本研究工作提出的Bi-ADWA技术为高性能音频ADC芯片设计提供了新颖有效的解决方案,显著提升了芯片的线性度和音频处理质量。该成果不仅展示了合肥工业大学在模拟与混合信号集成电路设计领域的深厚积累,也为下一代智能语音前端、便携式高清音频设备等应用提供了关键芯片技术支撑。该研究得到了国家自然科学基金、安徽省自然科学基金等项目的支持。合肥工业大学为论文第一署名单位,我校微电子学院2022级博士研究生孙奥运为第一作者,张章教授为通讯作者。

文章链接:https://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=11262228

(文:张章 图:张章 审核:李正星)